P5 (마이크로아키텍처)

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

P5 마이크로아키텍처는 인텔이 1990년대에 개발한 펜티엄 프로세서의 기반이 된 아키텍처이다. 386 및 486 설계를 담당했던 팀에 의해 설계되었으며, 슈퍼스칼라 RISC 아키텍처를 활용하여 온칩 캐시, 부동 소수점, 분기 예측 기능을 갖추었다. 펜티엄은 60MHz와 66MHz로 출시되었으며, 이후 P54C, P54CQS, P54CS, P24T, P55C 등 다양한 코어와 스테핑으로 발전했다. P5 마이크로아키텍처는 경쟁사들의 펜티엄 호환 프로세서 출시와 FDIV 버그, F00F 버그와 같은 오류로 인해 영향을 받기도 했다.

더 읽어볼만한 페이지

- 슈퍼스칼라 마이크로프로세서 - 펜티엄 II

펜티엄 II는 인텔이 펜티엄 프로의 P6 마이크로아키텍처를 기반으로 개발하여 일반 소비자 시장을 공략하기 위해 CPU 코어와 캐시 메모리를 분리하고 슬롯 1 인터페이스를 도입, MMX 명령어 세트 추가, 16비트 코드 성능 개선 등을 특징으로 하는 x86 마이크로프로세서이다. - 슈퍼스칼라 마이크로프로세서 - 애슬론

AMD가 1999년부터 출시한 애슬론은 x86 아키텍처 기반의 데스크톱, 모바일용 마이크로프로세서 제품군으로, 인텔 펜티엄 III에 대항하기 위해 개발되어 K7, K8 등 다양한 아키텍처를 거치며 성능이 향상되었고 슬롯 A에서 소켓 A, 소켓 AM4 등으로 인터페이스가 변경되었다. - 1993년 도입 - 체코 코루나

체코 코루나는 체코 공화국의 공식 통화로, 체코슬로바키아 해체 후 도입되었으며, 한때 수출 경쟁력 강화를 위한 약세 정책을 시행했으나 현재는 시장 환율 체제를 따르고 있으며, 유로화 도입 논의는 있지만 국민 여론으로 인해 계획은 없는 상태에서 동전과 지폐 형태로 발행되고 있다. - 1993년 도입 - 에어버스 A340

에어버스 A340은 에어버스가 개발한 4개의 터보팬 엔진을 장착한 장거리용 광동체 여객기로, A330과 부품을 공유하며, 1987년에 처음 출시되어 377대가 생산되었으나 낮은 연료 효율성으로 2011년에 생산이 종료되었다. - 인텔 마이크로아키텍처 - 그레이스몬트 (마이크로아키텍처)

그레이스몬트는 인텔 7 제조 공정을 기반으로 하여 향상된 명령어 처리 능력, 확장된 캐시 메모리, 개선된 분기 예측 기능 등을 제공하는 4세대 저전력 아톰 마이크로아키텍처이며, 앨더 레이크와 랩터 레이크 하이브리드 프로세서의 효율 코어 및 앨더 레이크-N 라인업의 코어 클러스터로 사용된다. - 인텔 마이크로아키텍처 - 넷버스트

넷버스트는 인텔이 더 높은 클럭 속도와 새로운 명령어 세트를 목표로 개발했으나 높은 발열과 전력 소비 문제로 중단된 마이크로아키텍처로, 펜티엄 4와 펜티엄 D 프로세서에 적용되었다.

| P5 (마이크로아키텍처) | |

|---|---|

| Pentium (i586) 정보 | |

| 이름 | 펜티엄 (i586) |

| |

| 모델 | 펜티엄 |

| 모델 2 | 펜티엄 오버드라이브 |

| 생산 시작 | 1993년 3월 22일 |

| 생산 종료 | 1999년 7월 15일 |

| 코어 수 | 1 |

| 트랜지스터 수 | 310만개 800 nm (P5) |

| 트랜지스터 수 1 | 320만개 600 nm (P54C) |

| 트랜지스터 수 2 | 330만개 350 nm (P54CS) |

| 트랜지스터 수 3 | 450만개 350 nm (P55C) |

| L1 캐시 | 16–32 KiB |

| L2 캐시 | 최대 512 KiB |

| 아키텍처 | x86-16, IA-32 |

| 마이크로아키텍처 | P5 |

| 확장 기능 | MMX |

| 소켓 1 | 소켓 4 |

| 소켓 2 | 소켓 5 |

| 소켓 3 | 소켓 7 |

| 이전 제품 | i486 |

| 다음 제품 | P6, 펜티엄 II, 펜티엄 III (SSE 후속) |

| 지원 상태 | 지원 중단 |

| 제조사 | 인텔 |

| 설계 회사 | 인텔 |

| 제조 회사 1 | 인텔 |

| 코드명 | 80501 (P5) |

| 코드명 2 | 80502 (P45C, P54CQS, P54CS) |

| 코드명 3 | 80503 (P55C, Tillamook) |

| 제조 공정 크기 (최소) | 800 nm |

| 제조 공정 크기 (최대) | 250 nm |

| 모델 3 | 펜티엄 MMX |

| 코어 1 | P5 |

| 코어 2 | P54C |

| 코어 3 | P54CQS |

| 코어 4 | P54LM |

| 코어 5 | P54CS |

| 코어 6 | P55C |

| 코어 7 | P55LM |

| 코어 8 | Tillamook |

| 코어 9 | P24T |

| 클럭 속도 (최저) | 60 MHz |

| FSB (최저) | 50 MHz |

| 클럭 속도 (최고) | 300 MHz |

| FSB (최고) | 66 MHz |

2. 역사

P5 펜티엄은 최초의 슈퍼스칼라 x86 프로세서로, 동시에 두 개의 명령어를 실행할 수 있었다. 구현에 사용된 일부 기술은 이전 슈퍼스칼라 인텔 i960 CA (1989)를 기반으로 했지만, 다른 세부 사항은 P5 설계를 위해 개발되었다. i386 또는 i486에서 많은 부분이 복사되었으며, 특히 파이프라인 방식으로 복잡한 x86 인코딩에 대처하는 데 사용된 전략이 그러했다.[8] i486과 마찬가지로 펜티엄은 특정 명령어 또는 명령어의 일부에 따라 최적화된 마이크로코드 시스템과 RISC와 유사한 기술을 모두 사용했다. 이중 정수 파이프라인 설계는 특정 학자 및 RISC 경쟁자들이 CISC 명령어 집합에서 구현하는 것이 불가능하다고 주장했던 것이다.

다른 주요 기능으로는 재설계되고 훨씬 빠른 부동 소수점 장치, 넓은 64비트 데이터 버스 (외부 및 내부), 별도의 코드 및 데이터 캐시 등이 있다.

P5는 i486에 비해 멀티프로세싱을 더 잘 지원하며, IBM 메인프레임 컴퓨터와 유사한 하드웨어 지원을 갖춘 최초의 x86 CPU이다. 인텔은 IBM과 협력하여 이 기능을 정의하고 P5 마이크로아키텍처에 이를 설계했다.

특정 컴파일러가 명령어 수준 병렬성을 더 잘 활용하도록 최적화되었지만, 모든 애플리케이션이 재컴파일로 인해 실질적인 이점을 얻는 것은 아니었다. 더 빠른 FPU는 i486 또는 i387에 비해 부동 소수점 성능을 항상 크게 향상시켰다. 인텔은 개발 도구 공급업체, ISV 및 운영 체제 (OS) 회사와 협력하여 제품을 최적화했다.

경쟁사로는 슈퍼스칼라 파워PC 601 (1993), 슈퍼스파크 (1992), DEC 알파 21064 (1992), AMD 29050 (1990), 모토로라 MC88110 (1991) 및 모토로라 68060 (1994) 등이 있었는데, 이들 대부분은 슈퍼스칼라 순차적 이중 명령어 파이프라인 구성을 사용했으며, 비 슈퍼스칼라 모토로라 68040 (1990) 및 MIPS R4000 (1991)도 있었다.

2. 1. 개발 배경

인텔은 1980년대 후반부터 386, 486 프로세서를 연이어 출시하며 PC 시장을 주도했다. 그러나 경쟁사들의 추격과 기술 발전 속도에 발맞춰 새로운 아키텍처의 프로세서 개발이 필요했다. 이에 인텔은 1989년부터 P5라는 코드명으로 펜티엄 프로세서 개발에 착수했다.[9]P5 마이크로아키텍처는 386 및 486을 설계한 산타클라라 팀이 설계했다.[9] 1989년에 설계 작업이 시작되었으며,[10] 팀은 수퍼스칼라 RISC 아키텍처를 사용하고, 온칩 캐시, 부동 소수점 및 분기 예측 기능을 갖추기로 결정했다.[11] 1990년에 예비 설계가 처음으로 성공적으로 시뮬레이션되었으며, 그 후 설계의 집적 회로 레이아웃이 이루어졌다. 당시 팀에는 수십 명의 엔지니어가 있었다. 1992년 4월에 설계가 테이프 아웃되었고, 베타 테스트가 시작되었다.[12] 1992년 중반까지 P5 팀에는 200명의 엔지니어가 있었다.[10] 인텔은 처음에 1992년 6월 PC 엑스포 무역 박람회에서 P5를 시연하고, 1992년 9월에 프로세서를 공식 발표할 계획이었지만,[13] 설계 문제로 인해 시연이 취소되었고, 칩의 공식 출시는 1993년 봄까지 연기되었다.[14][15]

존 H. 크로포드는 386의 수석 설계자였으며, 도널드 앨퍼트와 함께 P5 설계를 공동 관리했다.[16] 앨퍼트는 아키텍처 팀을 관리했고, 드로르 아브논은 FPU 설계를 관리했다.[17] 비노드 K. 담은 P5 그룹의 총괄 매니저였다.[10]

인텔은 1991년에 "386" 상표권 분쟁에서 패소하여 숫자가 일반 상표로 판결되었기 때문에 586 대신 펜티엄이라는 이름을 사용했다.

2. 2. 개발 과정

P5 마이크로아키텍처는 386 및 486을 설계한 산타클라라 팀이 설계하였다.[9] 1989년에 설계 작업이 시작되었으며,[10] 팀은 RISC와 CISC 기술을 융합한 슈퍼스칼라 RISC 아키텍처를 사용하고, 온칩 캐시, 부동소수점, 분기 예측 기능을 갖추기로 결정했다.[11] 1990년에 예비 설계가 처음으로 성공적인 시뮬레이션을 거쳤고, 이후 설계의 집적 회로 레이아웃이 진행되었다. 당시 팀에는 수십 명의 엔지니어가 있었다. 1992년 4월에 설계가 테이프 아웃되어 실리콘으로 이전되었고, 베타 테스트가 시작되었다.[12] 1992년 중반까지 P5 팀에는 200명의 엔지니어가 있었다.[10] 인텔은 처음에 1992년 6월 PC 엑스포에서 P5를 시연하고, 1992년 9월에 프로세서를 공식 발표할 계획이었으나, 설계 문제로 인해 시연이 취소되었고, 칩의 공식 출시는 1993년 봄까지 연기되었다.[14][15]존 H. 크로포드는 원래 386의 수석 설계자였으며, 도널드 앨퍼트와 함께 P5의 설계를 공동 관리했다.[16] 앨퍼트는 아키텍처 팀을 관리했고, 드로르 아브논은 FPU 설계를 관리했다.[17] 비노드 K. 담은 P5 그룹의 총괄 매니저였다.[10]

인텔의 래러비 멀티코어 아키텍처 프로젝트는 P5 코어(P54C)에서 파생된 프로세서 코어를 사용하며, 멀티스레딩, 64비트 명령어 및 16바이트 너비의 벡터 처리 장치가 추가되었다.[18] 초기 아톰 프로세서 코어에 사용된 인텔의 저전력 본넬 마이크로아키텍처 또한 P5와 유사한 순차적 이중 파이프라인을 사용한다.[19]

인텔은 1991년에 "386" 상표권 분쟁에서 패소하여 숫자가 일반 상표로 판결되었기 때문에 586 대신 펜티엄이라는 이름을 사용했다. 인텔은 렉시콘 브랜딩에 숫자가 아닌 새로운 이름을 개발하도록 의뢰했다.[20]

3. 기술적 특징

P5 펜티엄은 최초의 슈퍼스칼라 x86 프로세서로, 동시에 두 개의 명령어를 실행할 수 있었다. 이는 이전 세대의 i960 CA (1989)에 사용된 일부 기술과 P5 설계를 위해 개발된 다른 세부 사항들을 기반으로 구현되었다. 특히 복잡한 x86 인코딩을 처리하는 데 사용된 전략은 i386 또는 i486에서 많은 부분을 복사했다.[8] 펜티엄은 i486과 마찬가지로 특정 명령어 또는 명령어의 일부에 따라 최적화된 마이크로코드 시스템과 RISC와 유사한 기술을 모두 사용했다.

주요 기능은 다음과 같다.

- 재설계되고 훨씬 빨라진 부동 소수점 장치

- 64비트 데이터 버스 (외부 및 내부)

- 별도의 코드 및 데이터 캐시

P5는 i486에 비해 멀티프로세싱을 더 잘 지원하며, IBM 메인프레임 컴퓨터와 유사한 하드웨어 지원을 갖춘 최초의 x86 CPU이다. 인텔은 IBM과 협력하여 이 기능을 정의하고 P5 마이크로아키텍처에 설계했다.

이중 파이프라인을 최대한 활용하기 위해 특정 컴파일러가 명령어 수준 병렬성을 더 잘 활용하도록 최적화되었지만, 모든 애플리케이션이 재컴파일로 인해 실질적인 이점을 얻는 것은 아니었다. 인텔은 개발 도구 공급업체, ISV 및 운영 체제 (OS) 회사와 협력하여 제품을 최적화하는 데 자원을 투입했다.

P5 마이크로아키텍처는 이전 i486 아키텍처에 비해 다음과 같은 중요한 발전을 가져왔다.

- 성능 개선

- 64비트 외부 데이터 버스를 통해 메모리 접근 속도를 높였다.

- 코드와 데이터 캐시를 분리하여 캐시 충돌을 줄였다.

- 4-입력 주소 가산기를 사용하여 주소 계산 지연 시간을 줄였다.

- 마이크로코드를 최적화하여 REP MOVSW와 같은 반복 명령어와 CALL, RET, 시프트/회전 등의 일반 명령어 실행 속도를 높였다.

- 하드웨어 기반 곱셈기를 개선하여 MUL, IMUL 명령어 실행 속도를 높였다.

- 가상 8086 모드를 가속화하기 위한 가상화된 인터럽트를 지원한다.

펜티엄은 초당 1억 개 이상의 명령어 (MIPS)를 실행하도록 설계되었으며,[21] 75MHz 모델은 특정 벤치마크에서 126.5 MIPS에 도달할 수 있었다.[22]

3. 1. 슈퍼스칼라 아키텍처

펜티엄 프로세서는 인텔 x86 프로세서 중 최초로 슈퍼스칼라 아키텍처를 도입했다.[8] 이는 U, V로 명명된 두 개의 명령어 파이프라인을 통해 동시에 두 개의 명령어를 처리할 수 있도록 하여 성능을 획기적으로 향상시켰다. U 파이프라인은 모든 명령어를 처리할 수 있었고, V 파이프라인은 가장 일반적인 간단한 명령어를 처리할 수 있었다.일부 학자 및 RISC 경쟁자들은 CISC 명령어 집합에서 이중 파이프라인 설계 구현이 불가능하다고 주장했으나, 펜티엄은 이것이 가능함을 보여주었다.[8]

이러한 슈퍼스칼라 아키텍처의 도입으로 펜티엄은 이전의 486 프로세서에 비해 클럭 사이클당 거의 두 배의 성능을 제공했다.

3. 2. 부동 소수점 연산 장치(FPU) 개선

펜티엄 프로세서는 이전 486 프로세서에 비해 부동 소수점 연산 장치(FPU)를 크게 개선했다.[8] FPU의 재설계로 i486 또는 i387에 비해 부동 소수점 성능이 크게 향상되었다.[8] 인텔은 개발 도구 공급업체, ISV 및 운영 체제 (OS) 회사와 협력하여 제품을 최적화했다.[8]일부 명령어는 80486 FPU보다 최대 15배 높은 처리량을 보였으며, 특히 FMUL에서 큰 개선이 있었다. 펜티엄은 또한 일반(산술 또는 로드/저장) FPU 명령과 병렬로 FXCH ST(x) 명령을 실행할 수 있었다.[8]

3. 3. 기타 특징

P5 마이크로아키텍처는 이전 i486 아키텍처에 비해 다음과 같은 주요 기능들이 추가되었다.- 코드와 데이터 캐시 분리[8]

- 64비트 외부 데이터 버스[8]

- 멀티프로세싱 지원 강화[8]

- CPUID, CMPXCHG8B, RDTSC, RDMSR, WRMSR, RSM 등의 새로운 명령어 추가[8]

- 테스트 레지스터 TR0–TR7 및 액세스 명령 제거

- 프로세서 기반 디버그 포트 도입[8]

- L1 캐시 패리티 검사와 같은 자체 테스트 기능 향상[8]

이후 출시된 펜티엄 MMX는 MMX 명령어 집합을 추가하여 멀티미디어 애플리케이션의 성능을 향상시켰다.[8]

4. 코어 및 스테핑

펜티엄은 1990년대 중반 개인용 컴퓨터 시장에서 인텔의 주력 마이크로프로세서였다. 초기 디자인은 새로운 공정으로 재구현되었고, 경쟁력을 유지하고 특정 시장을 공략하기 위해 새로운 기능들이 추가되었다. 그 결과, P5 마이크로아키텍처에는 다양한 종류가 생겨났다.

- P5: 펜티엄 프로세서의 초기 모델이다. 슈퍼스칼라 x86 프로세서로, 동시에 두 개의 명령어를 실행할 수 있었다.[8]

- P54C: P5의 후속 제품으로, 전력 소비를 줄이기 위해 3.3V 전원을 사용한다.

- P54CQS: 350nm BiCMOS 공정으로 제조된 최초의 상용 마이크로프로세서이다.[25]

- P54CS: 소켓 7을 도입했다.[8]

- P24T: 486 시스템 업그레이드를 위한 펜티엄 오버드라이브 프로세서이다.

- P55C: '''MMX'''(명령 집합) 기술을 탑재한 펜티엄 (일반적으로 '''펜티엄 MMX'''라고만 불림)으로, 멀티미디어 작업의 성능을 향상시키기 위한 57개의 새로운 "MMX" 명령어 집합을 특징으로 했다.

- 틸라묵(Tillamook): 모바일 펜티엄 MMX 프로세서로, 저전력 설계를 통해 노트북 컴퓨터의 배터리 사용 시간을 늘렸다.[26]

P5 마이크로아키텍처는 386 및 486을 설계한 산타클라라 팀에 의해 설계되었다.[9] 설계 작업은 1989년에 시작되었으며,[10] 1992년 4월에 테이프 아웃되었고, 1993년 봄에 공식 출시되었다.[12] 존 H. 크로포드와 도널드 앨퍼트가 P5 설계를 공동 관리했다.[16]

인텔은 래러비 멀티코어 아키텍처 프로젝트에서 P5 코어(P54C)를 기반으로 한 프로세서 코어를 사용했으며, 초기 아톰 프로세서 코어에 사용된 본넬 마이크로아키텍처 또한 P5와 유사한 이중 파이프라인을 사용한다.[19]

인텔은 "386" 상표권 분쟁에서 패소하여 숫자가 일반 상표로 판결되었기 때문에 586 대신 펜티엄이라는 이름을 사용했다.[20]

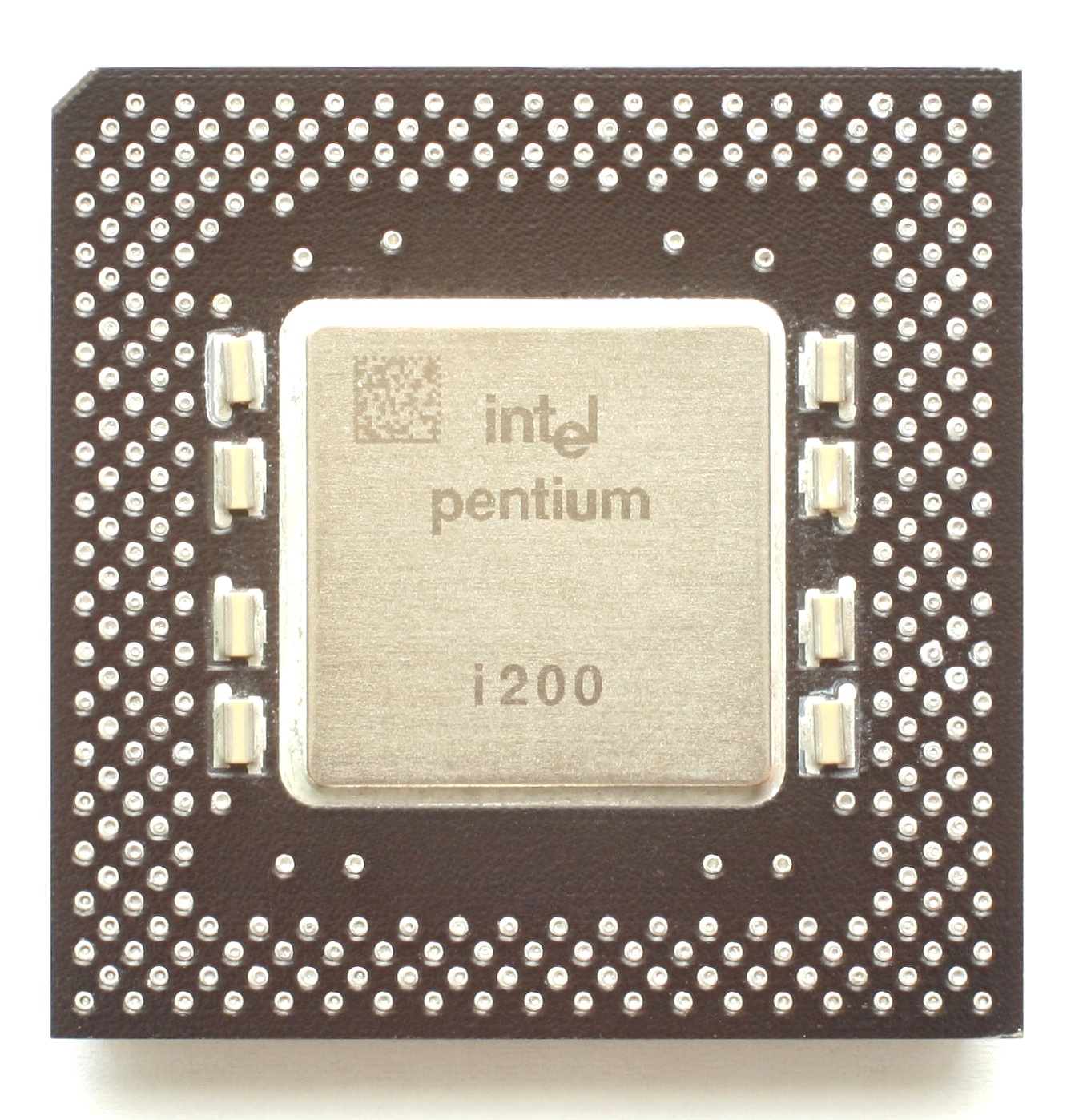

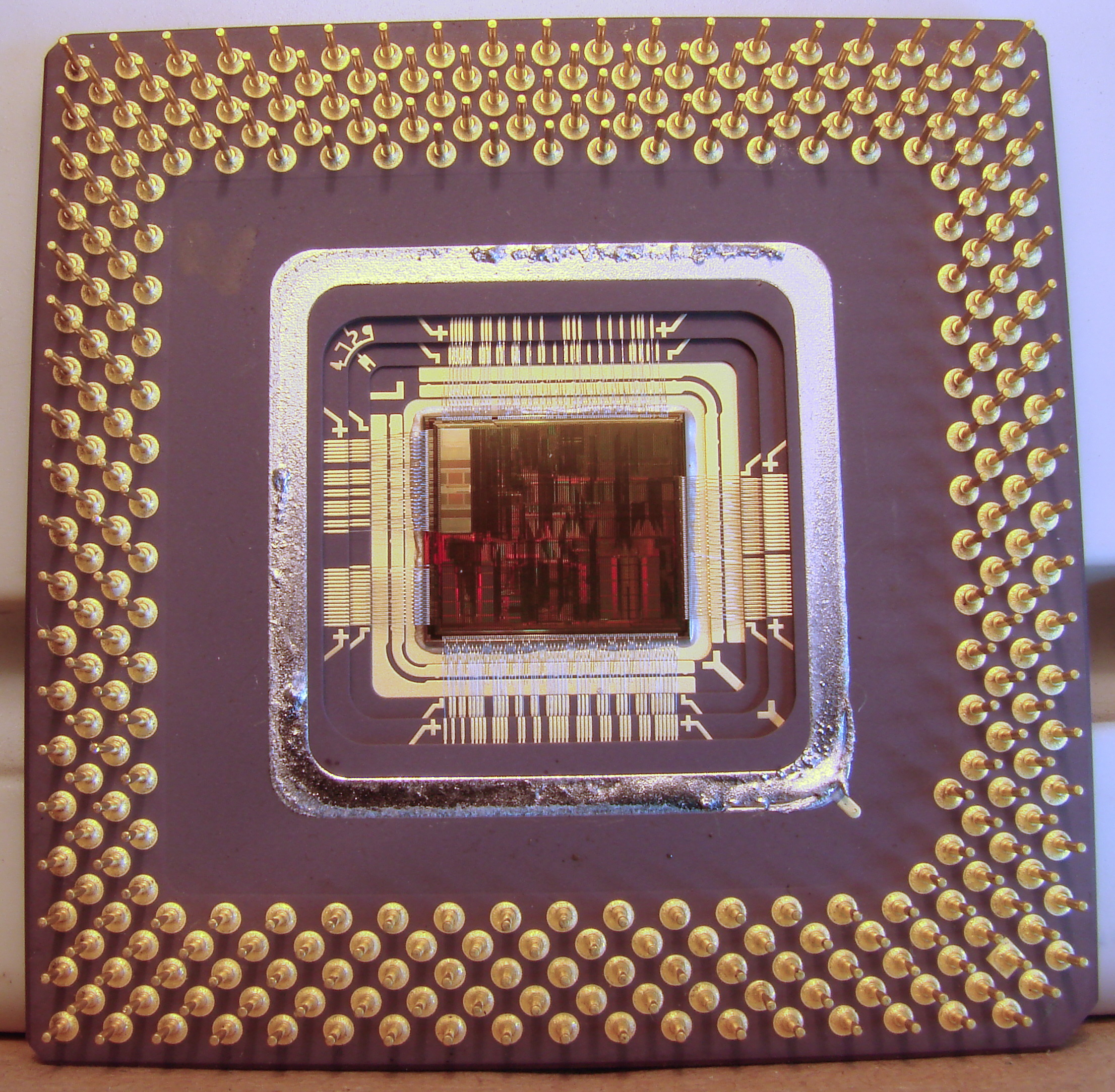

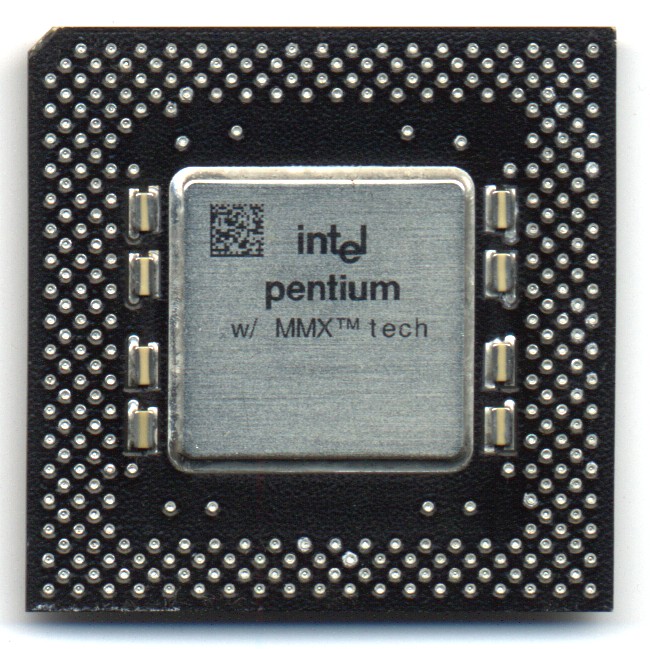

4. 1. P5

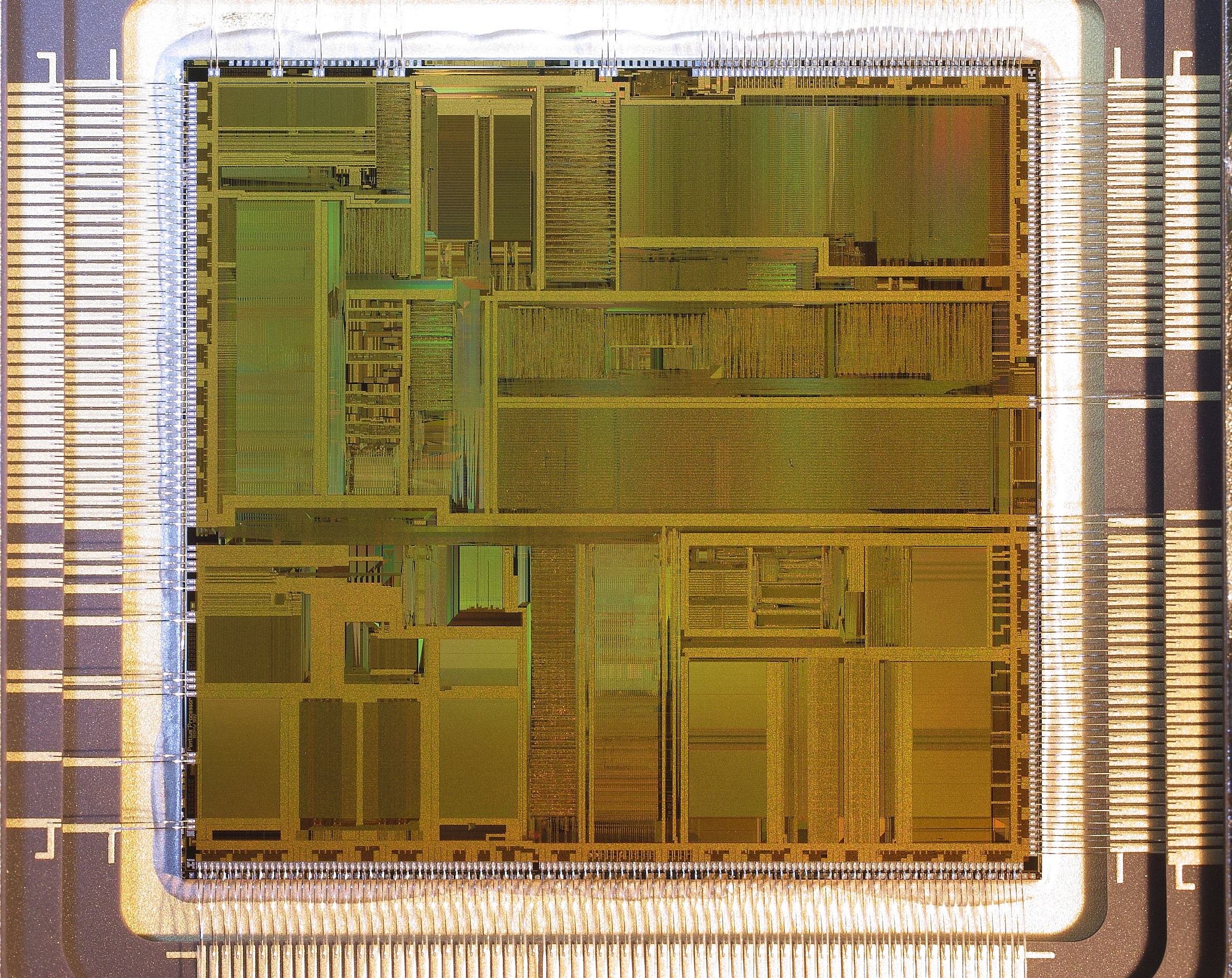

펜티엄 프로세서의 초기 모델은 60MHz와 66MHz 클럭 속도로 출시되었다. 이 프로세서는 800nm BiCMOS 공정으로 제조되었으며, 5V 전압에서 작동했다.[24] 310만 개의 트랜지스터를 포함하고 있으며, 다이 면적은 293.92mm2 (16.7mm x 17.6mm)였다.[23]P5 마이크로아키텍처는 이전의 i486 아키텍처에 비해 다음과 같은 주요 개선 사항을 포함한다.

- 성능 향상:

- 슈퍼스칼라 아키텍처: 펜티엄은 한 클럭 사이클에 두 개의 명령어를 실행할 수 있는 두 개의 파이프라인(U, V)을 가지고 있다.[8]

- 64비트 외부 데이터 버스: 메모리에서 읽거나 쓸 수 있는 정보량을 두 배로 늘려 코드 캐시 로딩 속도를 향상시켰다.

- 분리된 코드 및 데이터 캐시: 인출 및 피연산자 읽기/쓰기 충돌을 줄였다.

- 더 빠른 부동 소수점 장치: 일부 명령어는 80486 FPU보다 최대 15배 높은 처리량을 보였다.

- 4-입력 주소 가산기: 주소 계산 지연 시간을 줄였다.

- 마이크로코드 최적화: REP MOVSW와 같은 자동 반복 명령어의 성능을 향상시켰다.

- 가상 8086 모드 가속화: 가상화된 인터럽트를 통해 성능을 향상시켰다.

- 분기 예측 분기 예측 기능을 통해 성능을 향상시켰다.

- 기타 기능:

- 프로세서 기반 디버그 포트 도입

- 향상된 자체 테스트 기능

- 새로운 명령어 추가 (CPUID, CMPXCHG8B, RDTSC, RDMSR, WRMSR, RSM)

펜티엄은 초당 1억 개 이상의 명령어(MIPS)를 실행하도록 설계되었으며,[21] 75MHz 모델은 특정 벤치마크에서 126.5 MIPS에 도달했다.[22] 펜티엄 아키텍처는 일반적으로 486 프로세서보다 클럭 사이클 당 거의 두 배의 성능을 제공했다.

P5 칩은 소켓 4를 사용하며, 273핀 PGA 폼 팩터로 출시되었고, 5V 전원 공급 장치에서 작동했다.

|  | |

|---|---|---|

| 코드명 | P5 | |

| 제품 코드 | 80501 | |

| 공정 크기 | 800 nm | |

| 다이 면적 (mm2) | 293.92 (16.7 x 17.6) | |

| 트랜지스터 수 (백만 개) | 3.10 | |

| 소켓 | 소켓 4 | |

| 패키지 | CPGA/CPGA+IHS | |

| 클럭 속도 (MHz) | 60 | 66 |

| 버스 속도 (MHz) | 60 | 66 |

| L1 캐시 크기 | 8 KB 2-way set 연관 코드 캐시. 8 KB 2-way set 연관 쓰기-백 데이터 캐시 | |

| 코어 전압 | 5.0 | 5.15 |

| I/O 전압 | 5.0 | 5.15 |

| TDP (최대 W) | 14.6 (15.3) | 16.0 (17.3) |

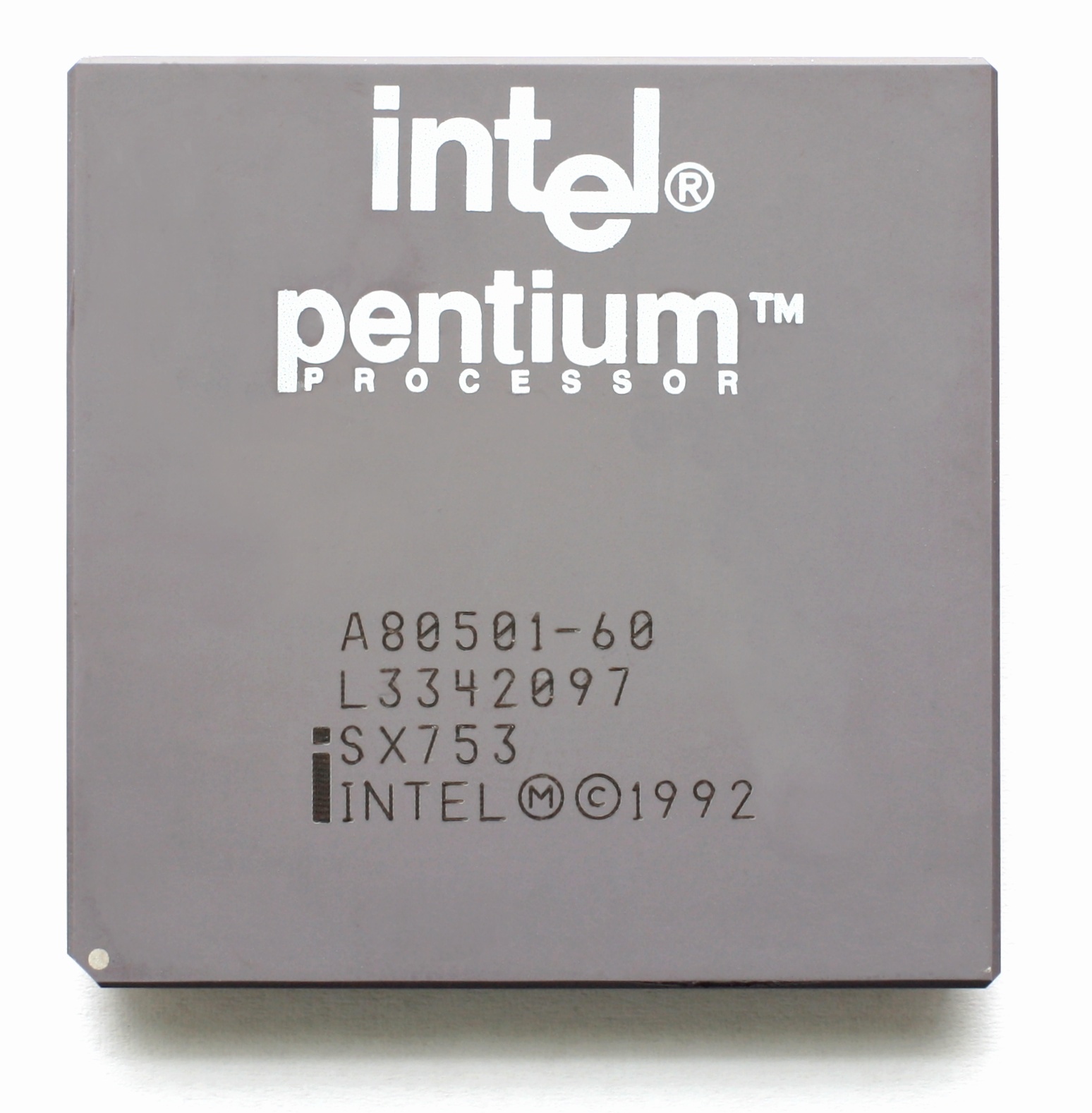

| 출시일 | 1993-03-22 | |

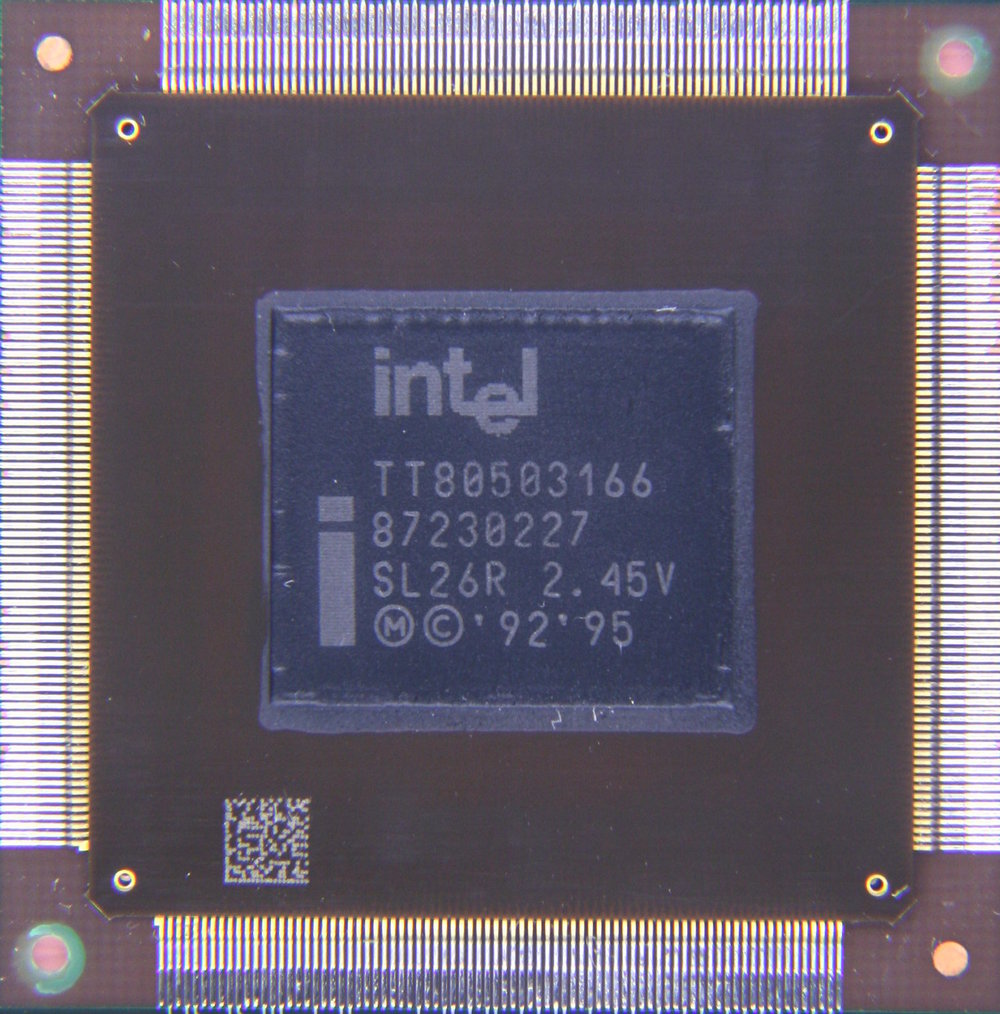

4. 2. P54C

P54C (80502)는 P5의 후속 제품으로, 1994년에 출시되었다. 75, 90, 100MHz의 클럭 속도로 작동하며, 3.3V 전원을 사용한다. 이는 전력 소비를 줄이기 위한 조치였지만, 메인보드에 전압 조절기가 필요했다.[25] 이 프로세서는 소켓 5를 사용하며, 내부 클럭 배율을 사용하여 외부 주소 및 데이터 버스보다 내부 회로가 더 높은 주파수로 작동하도록 했다. 이는 외부 주파수를 높이는 것이 물리적 제약으로 인해 더 복잡하고 번거롭기 때문이다.P54C는 양방향 멀티프로세싱을 지원하며, 통합 로컬 APIC와 새로운 전원 관리 기능을 갖추었다. 330만 개의 트랜지스터를 포함하고 있으며, 크기는 163mm2였다.[25] BiCMOS 공정으로 제작되었으며, 500nm와 600nm으로 묘사된다.[25]

P54C와 관련된 정보는 아래 표와 같다.

| P54C | ||||

| 제품 코드 | 80502 | |||

| 공정 크기 | 600 nm 또는 350 nm* | |||

| 다이 면적 (mm2) | 148 @ 600 nm / 91 (후기 83) @ 350 nm | |||

| 트랜지스터 수 (백만 개) | 3.20 | |||

| 소켓 | 소켓 5/7 | |||

| 패키지 | CPGA/CPGA+IHS/TCP* | |||

| 클럭 속도 (MHz) | 75 | 90 | 100 | |

| 버스 속도 (MHz) | 50 | 60 | 50 | 66 |

| L1 캐시 크기 | 8 KB 2-way set 연관 코드 캐시. 8 KB 2-way set 연관 쓰기-백 데이터 캐시 | |||

| 코어 전압 | 3.3 2.9* | 3.3 2.9* | 3.3 3.1* 2.9* | |

| I/O 전압 | 3.3 | |||

| TDP (최대 W) | 8.0 (9.5) 6.0* (7.3*) | 9.0 (10.6) 7.3* (8.8*) | 10.1 (11.7) 8.0 at 600nm* (9.8 at 600nm*) 5.9 at 35Onm* (7.6 at 350nm*) | |

| 출시일 | 1994-10-10 | 1994-03-07 | ||

| * 별표는 노트북용 모바일 펜티엄 또는 모바일 펜티엄 MMX 칩으로만 제공되었음을 나타냅니다. | ||||

4. 3. P54CQS

P54CQS는 1995년 초에 출시된 펜티엄 프로세서로, 120MHz의 클럭 속도로 작동한다. 이 프로세서는 350nm BiCMOS 공정으로 제조되었으며, 이는 상용 마이크로프로세서 중 최초였다.[25] 트랜지스터 수는 P54C와 동일하게 330만 개였으며, 새로운 공정에도 불구하고 다이 면적 역시 163mm2로 동일했다. 이는 칩 가장자리를 따라서만 연결을 허용하는 와이어 본딩 방식을 사용했기 때문이다. 만약 칩이 더 작아졌다면 와이어 길이에 제한이 있고 칩 가장자리가 패키지 패드에서 더 멀어지기 때문에 패키지를 다시 설계해야 했을 것이다. 따라서 칩 크기를 동일하게 유지하고 기존 패드 링을 유지하면서 펜티엄 로직 회로의 크기만 줄여 더 높은 클럭 주파수를 달성할 수 있도록 하였다.[25]4. 4. P54CS

P54CS는 133MHz, 150MHz, 166MHz, 200MHz 클럭 속도로 작동하는 모델이며, 소켓 7을 도입했다.[8]| 코드명 | P54CS | |||

|---|---|---|---|---|

| 제품 코드 | 80502 | |||

| 공정 크기 | 350 nm | |||

| 다이 면적 (mm2) | 91 (후기 83) | |||

| 트랜지스터 수 (백만 개) | 3.30 | |||

| 소켓 | 소켓 7 | |||

| 패키지 | CPGA/PPGA | |||

| 클럭 속도 (MHz) | 133 | 150 | 166 | 200 |

| 버스 속도 (MHz) | 60 | 66 | ||

| L1 캐시 크기 | 8 KB 2-way set 연관 코드 캐시. 8 KB 2-way set 연관 쓰기-백 데이터 캐시 | |||

| 코어 전압 | 3.3 | |||

| I/O 전압 | 3.3 | |||

| TDP (최대 W) | 11.2 (12.2) | 11.6 (13.9) | 14.5 (15.3) | 15.5 (16.6) |

| 출시일 | 1995-06-12 | 1996-01-04 | 1996-06-10 | |

| ||||

4. 5. P24T (펜티엄 오버드라이브)

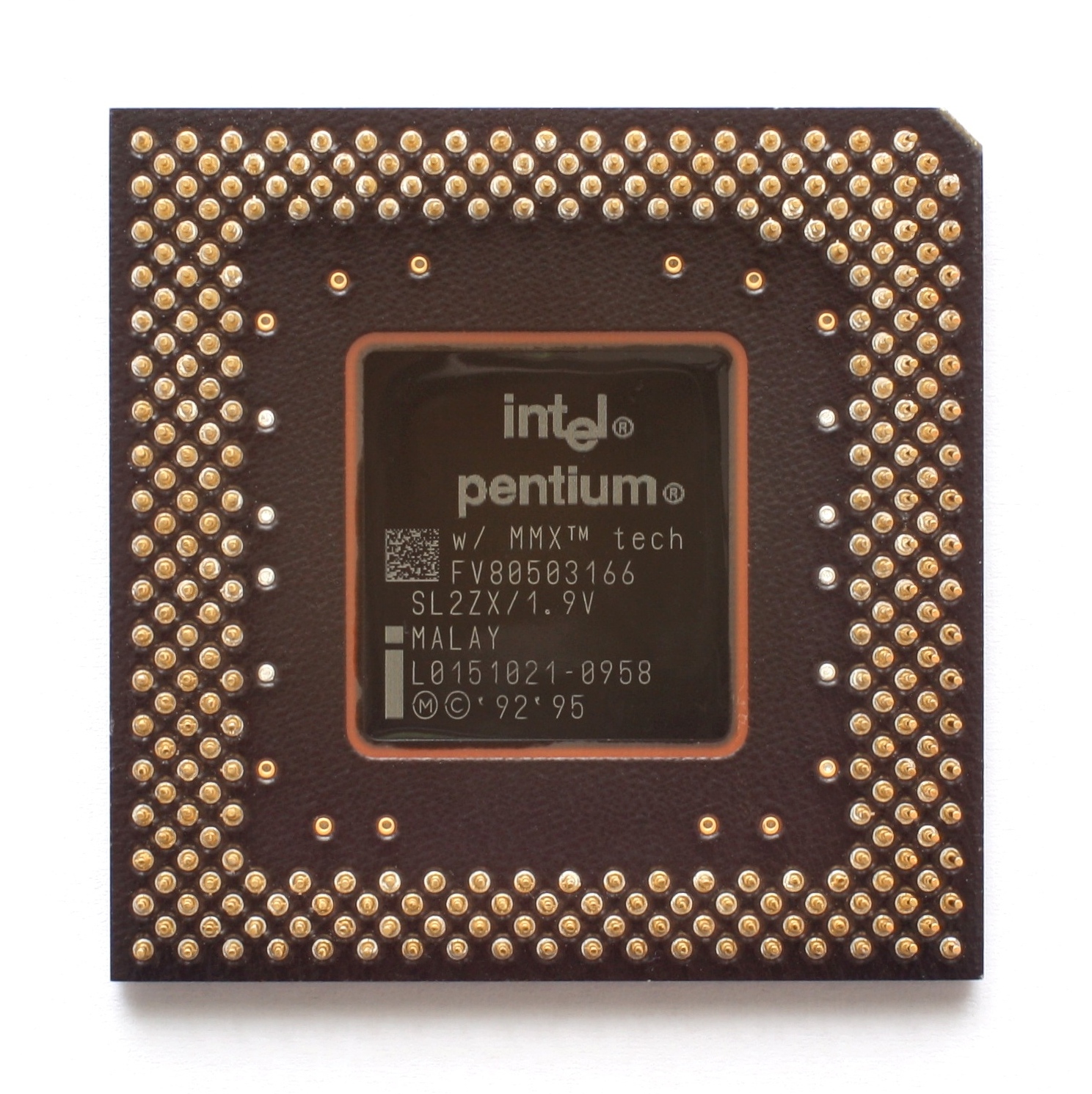

486 시스템 업그레이드를 위해 1995년에 출시된 펜티엄 오버드라이브는 3.3V 600nm 공정을 사용하여 63MHz 또는 83MHz 클럭으로 작동했다. 소켓 2/3을 사용했기 때문에, 486 마더보드의 32비트 데이터 버스와 느린 온보드 L2 캐시를 보완하기 위해 일부 수정이 필요했다. 따라서 32 KB L1 캐시(P55C 이전 펜티엄 CPU의 두 배)를 장착하여 486 시스템의 성능을 향상시켰다.[1]4. 6. P55C (펜티엄 MMX)

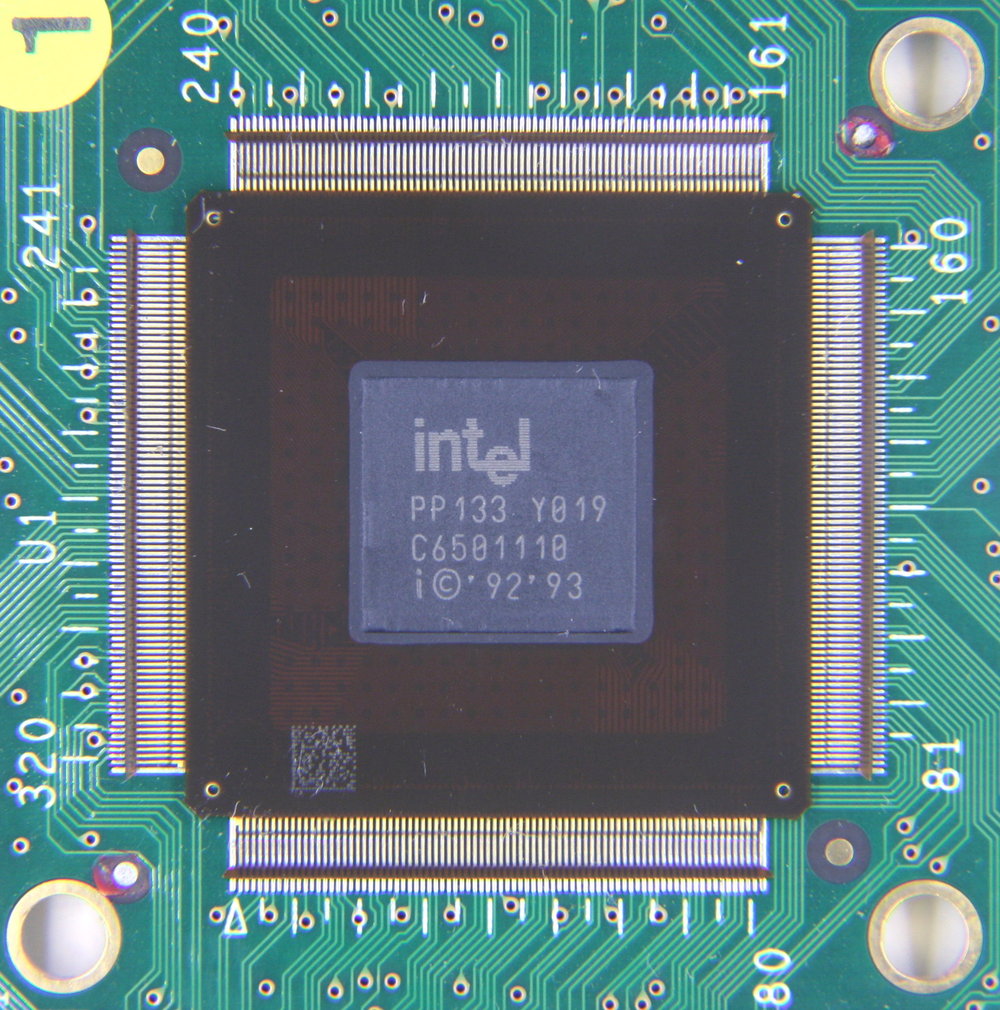

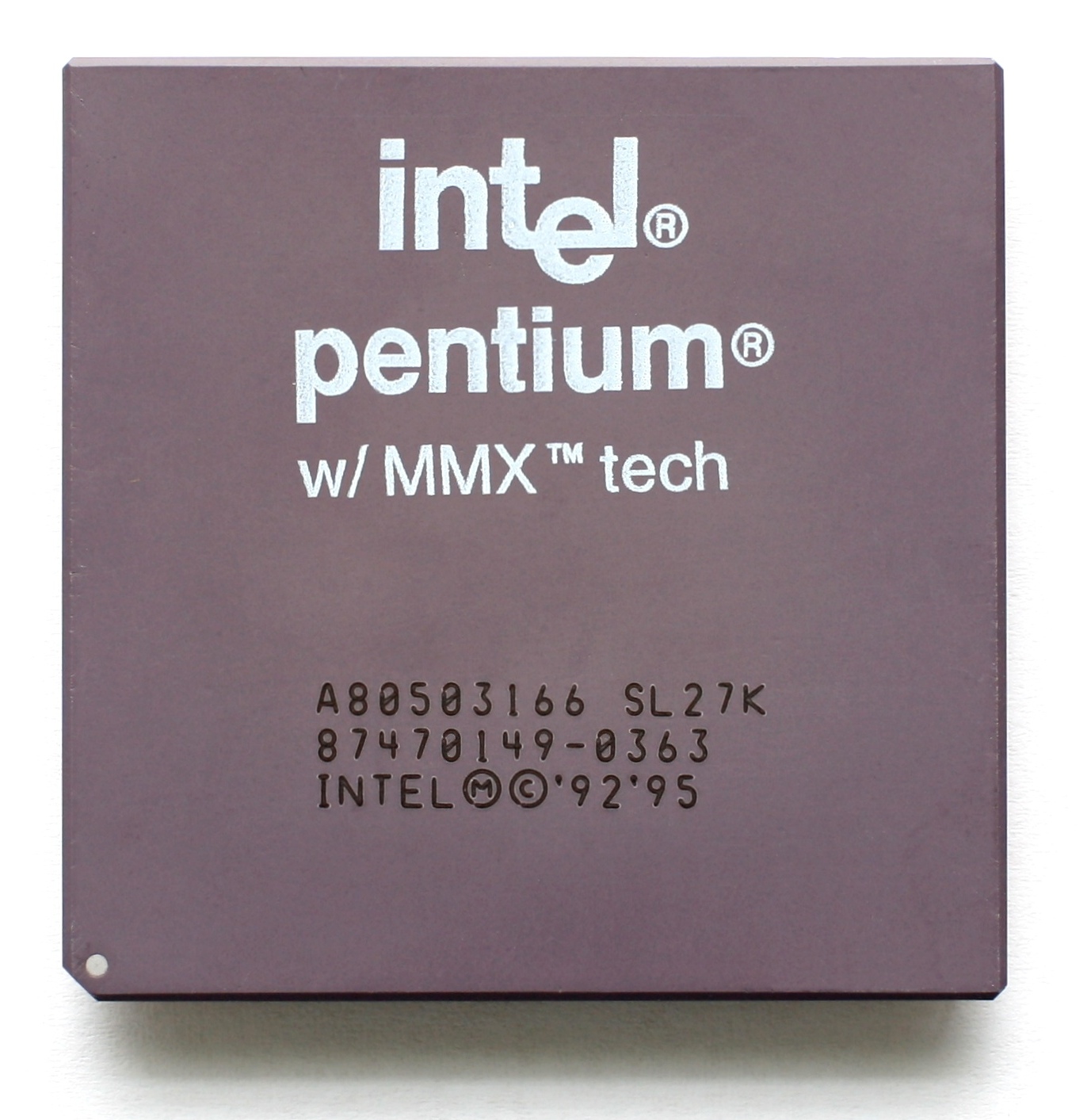

P55C (또는 80503)는 이스라엘 하이파에 있는 인텔 연구 개발 센터에서 개발되었다.[26] 이 칩은 '''MMX(명령 집합)''' 기술을 탑재한 펜티엄 (일반적으로 '''펜티엄 MMX'''라고만 불림)으로 판매되었으며, P5 코어를 기반으로 했지만, 디지털 미디어 데이터를 인코딩 및 디코딩하는 것과 같은 멀티미디어 작업의 성능을 향상시키기 위한 57개의 새로운 "MMX" 명령어 집합을 특징으로 했다. 펜티엄 MMX 라인은 1996년 10월 22일에 소개되었고, 1997년 1월에 출시되었다.[26]새로운 명령은 새로운 데이터 유형에서 작동했다. 즉, 8개의 8비트 정수, 4개의 16비트 정수, 2개의 32비트 정수 또는 1개의 64비트 정수로 구성된 64비트 묶음 벡터였다. 예를 들어, PADDUSB(Packed Add Unsigned Saturated Bytes) 명령은 각각 8개의 8비트 부호 없는 정수를 포함하는 두 개의 벡터를 요소별로 더한다. 산술 오버플로가 발생하여 포화 산술이 발생할 경우, 바이트로 표현할 수 있는 최대 부호 없는 값인 255가 생성된다.

코어의 다른 변경 사항으로는 반환 스택(Cyrix 6x86에서 처음 구현)과 더 나은 병렬 처리를 갖춘 6단계 파이프라인(P5에서는 5단계), 개선된 명령 디코더, 16KB L1 데이터 캐시 + 16KB L1 명령 캐시 (P5에서는 8KB L1 데이터/명령어 캐시, 2방향)와 4개의 쓰기 버퍼(P5에서는 각 파이프라인에 하나씩 해당)가 있으며, 개선된 분기 예측기는 펜티엄 프로에서 가져왔다.[27][28] 버퍼는 512개 항목을 가진다(P5에서는 256개).[29]

450만 개의 트랜지스터를 포함하고 있으며, 면적은 140mm2이다. 이전 350nm BiCMOS 공정과 동일한 금속 피치를 가진 280nm CMOS 공정으로 제조되었기 때문에 인텔은 유사한 트랜지스터 밀도를 이유로 "350nm"으로 설명했다.[30] 이 프로세스에는 4개의 상호 연결 레벨이 있다.[30]

P55C는 소켓 7과 호환되었지만, 칩 전원 공급을 위한 전압 요구 사항은 표준 소켓 7 사양과 달랐다. P55C 표준이 제정되기 전에 소켓 7용으로 제조된 대부분의 마더보드는 이 CPU의 적절한 작동에 필요한 이중 전압 레일(2.8V 코어 전압, 3.3V 입출력 (I/O) 전압)을 준수하지 않았다. 인텔은 자체 전압 조절 기능을 갖춘 인터포저를 특징으로 하는 오버드라이브 업그레이드 키트로 이 문제를 해결했다.

| ||||||

| 코드명 | P55C | |||||

| 제품 코드 | 80503 | |||||

| 공정 크기 | 350 nm (후기 280 nm) | |||||

| 다이 면적 (mm2) | 141 @ 350 nm / 128 @ 280 nm | |||||

| 트랜지스터 수 (백만 개) | 4.50 | |||||

| 소켓 | 소켓 7 | |||||

| 패키지 | TCP* | CPGA/PPGA/TCP* | PPGA/TCP* | |||

| 클럭 속도 (MHz) | 120* | 133* | 150* | 166 | 200 | 233 |

| 버스 속도 (MHz) | 60 | 66 | 60 | 66 | ||

| L1 캐시 크기 | 16 KB 4-way set 연관 코드 캐시. 16 KB 4-way set 연관 쓰기-백 데이터 캐시 | |||||

| 코어 전압 | 2.2* | 2.45* | 2.45* | 2.8/2.45* | 2.8 | 2.8 |

| I/O 전압 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 | 3.3 |

| TDP (최대 W) | 4.2* | 7.8* (11.8*) | 8.6* (12.7*) | 13.1 (15.7) 9.0* (13.7*) | 15.7 (18.9) | 17.0 (21.5) |

| 출시일 | 1996-10-20 | 1997-05-19 | 1997-01-08 | 1997-06-02 | ||

| * 별표는 노트북용 모바일 펜티엄 또는 모바일 펜티엄 MMX 칩으로만 제공되었음을 나타냅니다. | ||||||

| ||||||

| 코드명 | P54CTB | |||||

| 제품 코드 | PODPMT60X150 | PODPMT66X166 | PODPMT60X180 | PODPMT66X200 | ||

| 공정 크기 (nm) | 350 | |||||

| 소켓 | 소켓 5/7 | |||||

| 패키지 | 방열판, 팬 및 전압 조절기가 있는 CPGA | |||||

| 클럭 속도 (MHz) | 125 | 150 | 166 | 150 | 180 | 200 |

| 버스 속도 (MHz) | 50 | 60 | 66 | 50 | 60 | 66 |

| 업그레이드 대상 | 펜티엄 75 | 펜티엄 90 | 펜티엄 100 및 133 | 펜티엄 75 | 펜티엄 90, 120 및 150 | 펜티엄 100, 133 및 166 |

| TDP (최대 W) | 15.6 | 15.6 | 15.6 | 18 | ||

| 전압 | 3.3 | 3.3 | 3.3 | 3.3 | ||

|  | ||||

| 코드명 | P55C | ||||

| 제품 코드 | FV8050366200 | FV8050366233 | FV80503CSM66166 | GC80503CSM66166 | GC80503CS166EXT |

| 공정 크기 (nm) | 350 | ||||

| 클럭 속도 (MHz) | 200 | 233 | 166 | 166 | 166 |

| 버스 속도 (MHz) | 66 | 66 | 66 | 66 | 66 |

| 패키지 | PPGA | PPGA | PPGA | BGA | BGA |

| TDP (최대 W) | 15.7 | 17 | 4.5 | 4.1 | 4.1 |

| 전압 | 2.8 | 2.8 | 1.9 | 1.8 | 1.8 |

4. 7. 틸라묵 (Tillamook)

틸라묵(Tillamook)은 모바일 펜티엄 MMX 프로세서로, 250nm 공정으로 제조되었다. 이름을 오리건 주의 도시에서 따왔다. 저전력 설계를 통해 노트북 컴퓨터의 배터리 사용 시간을 늘렸다.[26] 틸라묵 모바일 펜티엄 MMX는 시스템의 512KB 정적 램(SRAM) 캐시 메모리와 함께 430TX 칩셋을 포함하기도 했다.[30]| 코드명 | 틸라묵 |

|---|---|

| 제품 코드 | 80503 |

| 공정 크기 | 250 nm |

| 다이 면적 (mm2) | 94.47 (9.06272 x 10.42416 mm) |

| 트랜지스터 수 (백만 개) | 4.50 |

| 패키지 | TCP/TCP on MMC-1 |

| 클럭 속도 (MHz) | 166, 200, 233, 266, 300 |

| 버스 속도 (MHz) | 66 |

| L1 캐시 크기 | 16 KB 4-way set 연관 코드 캐시. 16 KB 4-way set 연관 쓰기-백 데이터 캐시 |

| 코어 전압 | 1.9, 1.8*, 2.0* |

| I/O 전압 | 2.5 |

| TDP (최대 W) | 4.5 (7.4) 4.1* (5.4*), 5.0* (6.1*), 5.5* (7.0*), 7.6 (9.2) 7.6* (9.6*), 8.0* |

| 출시일 | 1997-08, 1998-01, 1999-01 |

| * 별표는 노트북용 모바일 펜티엄 또는 모바일 펜티엄 MMX 칩으로만 제공되었음을 나타냅니다. | |

| 코드명 | 틸라묵 |

|---|---|

| 제품 코드 | FV80503CSM66166, GC80503CSM66166, GC80503CS166EXT, FV80503CSM66266, GC80503CSM66266 |

| 공정 크기 (nm) | 250 |

| 클럭 속도 (MHz) | 166, 266 |

| 버스 속도 (MHz) | 66 |

| 패키지 | PPGA, BGA |

| TDP (최대 W) | 4.5, 4.1, 7.6 |

| 전압 | 1.9, 1.8, 2.0 |

5. 경쟁 제품

펜티엄이 출시된 후, 넥스젠(NexGen),[31] AMD, 사이릭스(Cyrix), 텍사스 인스트루먼트(Texas Instruments) 등 경쟁사들이 1994년에 펜티엄 호환 프로세서를 발표했다.[32] AMD와 인텔의 프로세서는 오리지널 펜티엄과의 호환성을 유지한다.

- WinChip C6

- 라이즈(Rise) mP6

5. 1. AMD K5, K6

AMD는 펜티엄 프로세서에 대항하기 위해 AMD K5를 출시했으나, 설계상의 어려움으로 인해 출시가 지연되었다.[34] 이후 AMD는 넥스젠(NexGen)을 인수하여 AMD K6 설계를 완성했다.[34] AMD와 인텔의 프로세서는 오리지널 펜티엄과의 호환성을 유지한다.5. 2. Cyrix 6x86

사이릭스(Cyrix)는 6x86 프로세서를 통해 펜티엄과 경쟁했다.[32] PC 매거진(PC Magazine)은 사이릭스 6x86을 펜티엄과 호환되는 프로세서 중 최초로 출시된 제품으로 평가했다.[34] 이후 사이릭스는 내셔널 세미컨덕터(National Semiconductor)에 인수되었다.5. 3. NexGen Nx586

넥스젠(NexGen)은 Nx586 프로세서를 통해 펜티엄과 경쟁했다.[31] ''CIO 매거진(CIO magazine)''은 Nx586을 펜티엄과 호환되는 최초의 CPU 중 하나로 언급했다.[33]6. 오류 (Errata)

초기 버전(60–66MHz) P5 펜티엄 프로세서에는 일부 나눗셈 연산에서 부정확하지만 예측 가능한 결과를 초래하는 부동 소수점 장치(FPU)에 문제가 있었다. 이 결함은 펜티엄 FDIV 버그로 널리 알려졌으며, 인텔에 큰 망신을 안겨주어 결함이 있는 프로세서를 교체하는 프로그램을 만들어야 했다.

1997년에는 "F00F 버그"라는 또 다른 오류가 발견되었다. 모든 P5 시리즈 프로세서가 이 오류의 영향을 받았으나, 당시 운영 체제는 시스템 충돌을 방지하기 위한 해결책으로 패치되었다.

6. 1. 펜티엄 FDIV 버그

펜티엄 FDIV 버그는 1994년 버지니아주 린치버그 칼리지의 토마스 나이슬리 교수가 발견한 초기 버전(60–66MHz) P5 펜티엄 프로세서의 부동 소수점 장치(FPU) 오류이다. 이 버그는 일부 나눗셈 연산에서 부정확하지만 예측 가능한 결과를 초래했다. 이 문제는 인텔에 큰 망신을 안겨주었고, 결국 인텔은 결함이 있는 프로세서를 교체하는 프로그램을 운영해야 했다.1997년에는 "F00F 버그"라는 또 다른 오류가 발견되었다. 이 버그는 악성 프로그램이 특별한 권한 없이 시스템을 다운시킬 수 있게 하는 문제였다. 모든 P5 시리즈 프로세서가 이 문제의 영향을 받았으며, 수정된 스테핑은 출시되지 않았다. 그러나 당시 운영 체제는 이러한 다운 현상을 방지하기 위한 해결책으로 패치되었다.

6. 2. 펜티엄 F00F 버그

1997년에 악성 코드가 특별한 권한 없이 시스템을 다운시킬 수 있는 F00F 버그가 발견되었다.[1] 모든 P5 시리즈 프로세서가 이 버그의 영향을 받았으며, 수정된 스테핑은 출시되지 않았다. 하지만, 당시 운영 체제는 이 문제를 해결하기 위해 패치를 배포했다.[1]7. 한국 사회에 끼친 영향

P5 (마이크로아키텍처)는 인텔에서 개발한 마이크로프로세서 아키텍처로, 펜티엄 프로세서에 적용되었다. 따라서 P5 마이크로아키텍처 자체가 직접적으로 한국 사회에 영향을 주었다기보다는, 펜티엄 프로세서를 통해 간접적인 영향을 미쳤다고 보는 것이 더 정확하다.

참조

[1]

웹사이트

Product Change Notification #777

http://developer.int[...]

Intel

1999-02-09

[2]

웹사이트

Intel® Pentium® Processor with MMX™ Technology 200 MHZ, 66 MHZ FSB - Product Specifications

https://www.intel.co[...]

[3]

간행물

View Processors Chronologically by Date of Introduction

http://www.intel.com[...]

Intel

2007-08-14

[4]

간행물

Intel Pentium Processor Family

http://www.intel.com[...]

Intel

2007-08-14

[5]

문서

I.e. 8086/88, 186/286, 386, 486, P5

[6]

웹사이트

The History Of Intel CPUs: Updated!

https://www.tomshard[...]

2018-09-08

[7]

문서

officially known as ''Pentium with MMX Technology''

[8]

문서

as compared to a simple RISC processor like the i960.

[9]

서적

The Pentium Chronicles: The People, Passion, and Politics Behind Intel's Landmark Chips

Wiley

2006

[10]

간행물

Inside Intel

1992-06-01

[11]

문서

House, Dave, "Putting the RISC vs. CISC Debate to Rest", Intel Corporation, Microcomputer Solutions, November/December 1991, page 18

[12]

간행물

The hot new star of microchips

http://www.iptegrity[...]

1993-05-01

[13]

간행물

Intel to offer a peek at its '586' chip

https://books.google[...]

1992-03-16

[14]

간행물

Design woes force Intel to cancel 586 chip demo

https://books.google[...]

1992-06-15

[15]

간행물

P5 chip delay won't alter rivals' plans

https://books.google[...]

1992-07-27

[16]

간행물

Intel Turns 35: Now What?

https://books.google[...]

2003-07-21

[17]

간행물

Architecture of the Pentium microprocessor]

https://ieeexplore.i[...]

1993-06

[18]

저널

Larrabee: A Many-Core x86 Architecture for Visual Computing

https://pages.cs.wis[...]

2023-08-18

[19]

간행물

Why Pine Trail Isn't Much Faster Than the First Atom

http://www.anandtech[...]

2010-08-04

[20]

뉴스

Why Intel Couldn't Trademark Numbers Anymore

https://www.vice.com[...]

2017-06-14

[21]

웹사이트

PC users guide: General Computer Information

http://dede.essortme[...]

2007-09-14

[22]

웹사이트

Chronology of Microprocessors

http://www.islandnet[...]

[23]

간행물

Intel Reveals Pentium Implementation Details

1993-03-29

[24]

웹사이트

Intel Pentium processor (510\60, 567\66). Nov 1994

http://datasheets.ch[...]

[25]

간행물

Pentium is First CPU to Reach 0.35 Micron

1995-03-27

[26]

간행물

New Chip Begs New Questions

http://news.cnet.com[...]

CNet

2009-02-06

[27]

웹사이트

Intel Architecture Optimization Manual

https://www.ece.cmu.[...]

2017-09-01

[28]

웹사이트

Phil Storrs PC Hardware book

http://philipstorr.i[...]

2017-09-01

[29]

웹사이트

Pentium Processor with MMX Technology

http://download.inte[...]

2017-09-01

[30]

간행물

Intel's Long-Awaited P55C Disclosed

1996-03-05

[31]

저널

NexGen to Beat Intel's Chip Prices

https://books.google[...]

International Data Group

1994-07-11

[32]

저널

Pentium Killers

https://books.google[...]

Ziff Davis

1994-01-11

[33]

저널

In the Chips

https://books.google[...]

International Data Group

1995-06-15

[34]

저널

The CPU for Your Next PC

https://books.google[...]

Ziff Davis

1997-09-23

[35]

인용

View Processors Chronologically by Date of Introduction:

http://www.intel.com[...]

Intel

[36]

인용

Intel Pentium Processor Family

http://www.intel.com[...]

Intel

2007-08-14

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com